# ARINC429 总线接口芯片及接口板的设计与实现

刘明东, 禄乐滨

(空军工程大学 电讯工程学院,陕西 西安 710077)

摘 要:通过对 ARINC429 总线的研究,设计了一种方法来接收 ARINC429 信号,该方法在接收 429 信号时将根据 429 信号的特征对 429 信号的每一位进行 3 次判别,只有当 3 次判别都正确时,才接收该位。该方法的抗干扰性优于传统方法。基于这种方法,用可编程逻辑器件设计制作了 AR-INC429 接口芯片,同时还制作可用于连接微机的接口板。

关键词:ARINC429;可编程逻辑器件;接口

中图分类号:TH113 文献标识码:A 文章编号:1009-3516(2001)01-0030-03

机载数据总线 ARINC429 在当代的运输机和相当数量的民航客机(如 A310, A300, A600, B757, B767 等)以及军用飞机中都得到广泛的应用。为了能够使微机与 ARINC429 总线相连并对机载设备进行检测和 仿真,该文设计制作了一种专用的接口芯片,并用该芯片制作了微机与 ARINC429 的接口板。

#### 1 ARINC429 总线简介

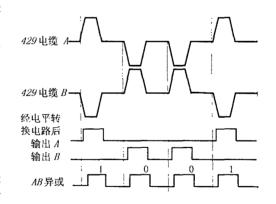

ARINC429 总线采用双绞屏蔽线传输信息。调制方式采用双极归零制的三态码方式,即信息由"高"、"零"和"低"状态组成的三电平状态调制。接收端高电平范围为  $6.5\sim13~V$ ,"零"电平范围为  $2.5\sim-2.5~V^{[1]}$ ,低电平范围为  $6.5\sim-13~V$ 。由于双绞线上的电平与 TTL 电平不一致,所以,先将双绞线上信号经

差放电平转换电路转换成 TTL 电平再由数字电路处理。429 电缆上信号及经电平转换电路后的信号如图 1 所示。429 总线的字同步是以传输周期间至少四位的时间间隔为基准,紧跟该字间隔后要发送的第一位的起点即为新字的起点。

## 2 一种接收 ARINC429 信号的方法

采用图 1 所示的双极归零码传递信号的一个好处 是可以在接收端方便地分离出数据时钟信号,即把两 个输入的 429 信号经电平转换后相异或,由此得到数 据时钟。以往的 429 信号接收就是用这样的方法,先得

图 1 429 信号以及电平转换后的波形

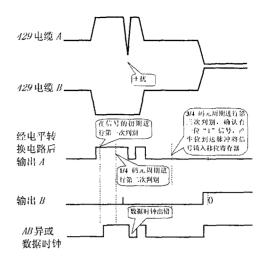

到数据时钟,然后用此时钟锁存数据。这种方法虽然简单,但也有不足之处,若 429 信号在传输过程中受到干扰,数据时钟就会出错,从而导致整个数据字不正确。为了避免这种缺欠,我们不采用这样的数据时钟来锁存数据。我们采用方法的基本思想是:使用 16 倍频的时钟对信号进行监测,电路将在每一位信号的初期、1/4 码元周期和 3/4 码元周期三个时刻对信号进行检测,每一位信号检测 3 次,只有当 3 次检测都符合 429 信号标准时才将该位锁入移位寄存器。具体过程如下:在检测电路检测到 A、B 信号中有一根线为高电平后(以 A 线为高电平为例),便启动时间计数器计数,根据计数器值,当到了该位的 1/4 周期时,再对 A、B 信号进行检

收稿日期:2000-04-25

测,若出现在 A、B 线上的是真正的信号,而不是干扰信号,此时 A 应在高电平, B 为低电平, 果真如此,则继续等待, 否则认为是干扰信号, 电路复位, 当到该位的 3/4 周期时, 再对 A、B 检测, 这时 A、B 应该为低电平, 若 A、B 果真均为低电平,则确认有一位"1"信号到达,产生一个位到达脉冲, 把该数据位锁入移位寄存器, 然后电路复位, 等待检测下一位, 否则认为是干扰信号, 电路复位。该电路能够有效地排除干扰信号, 比429 信号直接异或获得数据时钟的方法要稳定, 并且能放宽对 429 信号的要求。两种方法的波形的比较如图 2 所示。

由图 2 可见,只要干扰不出现在码元周期的 1/4 和 3/4 处,本文芯片的位判别逻辑就会正确判别。

图 2 两种方法的比较

### 3 ARINC429 接口芯片及接口板的实现

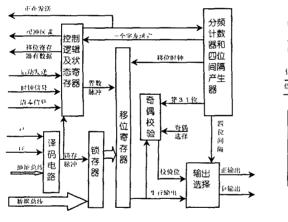

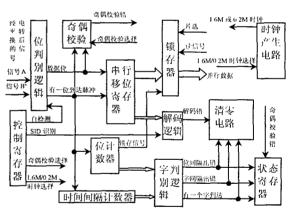

LATTICE 公司的 ispLSI 器件是一种在系统可编程的 CPLD 器件,它具有密度较高、在线可编程、开发方便等优点。我们选用一片 LATTICE 公司的 ispLSI 器件 ispLSI1048 完成了 429 接口芯片的制作。该接口芯片可发送和接收一路 429 数据,用户可用读写信号和少量的状态、控制信号完成对它的全部操作。按功能把芯片内的电路分为两个模块,发送器和接收器。各模块的结构如图 3、图 4 所示。

图 3 发送器框图

图 4 接收器框图

发送器:用户可将数据写入它的缓冲器,并通过状态位可判别它的工作状态(发送缓冲器空、正在发送和有数据可发),通过启动发送信号,控制发送数据。发送器可自动将缓冲器中的数据装入发送寄存器,发送器有一个32位的缓冲器和一个32位的移位寄存器,虽然它只有一个缓冲器,但它仍然可以连续地发送数据。

接收器:可接收经电平转换后的 32 位数据,用户通过读操作读出它所收到的数据,并且通过状态信号得知有无数据到达,接收正确与否。接收器对数据进行 16 倍频采样,并且对收到的每一数据位进行判别,以区分干扰信号和真正的数据信号,并自动对收到的数据实行差错控制,对于奇偶验出错、字间隔、位间隔出错等错误自动检测并保存于状态寄存器中,用户可通过写控制寄存器的方法对收发器的收发速率、奇偶校验、SID 识别、自检测状态、差错控制等进行设置。接收器各部分的作用如下:位判别逻辑用于对到达的每一位信号进行 3 次判别,若 3 次判别都符合 429 信号的标准,则把数据位锁入移位寄存器,若不符合则舍去。移位寄存器用于接收串行数据,位计数器用于计录移位寄存器中已收到的位数,每收到一个字后位计数器清零。时间间隔计数器用于计录每位到达的时间间隔,每当有一位到达后清零并开始计数。字判别逻辑根据位计数器和时间间隔计数器来判别是否有一字到达或有错误。清零电路在接收器收到一个字的数据和接收错误时对

#### 电路清零。

ARINC429 总线数据收发速率有两种,分别是:100 kbit/s 或 12.5 kbit/s。该芯片在接收数据时,为了保证接收数据的正确性,对接收数据进行 16 倍频的采样,所以该芯片的工作频率是 1.6 MHz 或 200 kHz,而 ispLS11048 芯片的最大工作频率 70 MHz 时,引脚至引脚间的最大延迟时间是 16 ns,所以选用 ispLSI1048 芯片足以胜任接收数据的工作<sup>[2]</sup>。有些飞机的 429 总线数据收发速率不标准,例如有的数据收发速率是 46 kbit/s,该芯片可以通过改变外部时钟或对时钟产生电路分频倍数重新编程来适应。经计算机模拟测试该芯片可以正确收发 ARINC429 总线的数据,且抗于扰性能较好。

该芯片与外界的连接信号有:数据线、地址线、写信号、读信号;状态信号有:发送缓冲器满、发送寄存器有数据、正在发送、接收到一个字等。为了减少连线,也可将状态信号存入状态寄存器,由数据线读出。由于该芯片可方便地与微机的总线相连,所以微机接口板的设计制作就比较容易。接口板上只需一块这样的芯片和电平转换电路即可。微机可以通过该接口板连接429线,对机载设备进行检测和仿真。

#### 参考文献:

- [1] 王 勇. ARINC 429 总线接口的设计[D]. 西安:空军工程大学工程学院. 1995.

- [2] LATTICE 半导体公司. ispLSI 1000EA Family[OL]. http://WWW. Latticesemi. com/Products/devices/isp1OOOea. htm. 1997-01-10.

# The design and realization of ARINC429 interface chip and interface card

LIU Ming-dong, LU Le-bin (The Telecommunication Engineering Institute, AFEU., Xi'an 710077, China)

Abstract. We design a method to receive ARINC429 signal. The main characteristic of this method is detect every bit of ARINC429 signal three times during receiving, only when all these three detections are right can the bit be received. This method is more reliable than traditional method. We designed and realized ARINC429 interface chip with PLD by this method, and made an interface card which can be used to connect microcomputers.

Key words · ARINC429; PLD; interface